This year, I organized a session on Quantum Computing at ISCAS 2019 in Japan!

The International Symposium on Circuits and Systems will be held in Sapporo, Japan, from May 26th to May 29th. The session titled “Towards Large-Scale Quantum Computers Session” will be held on May 28th at 14:50. More information here.

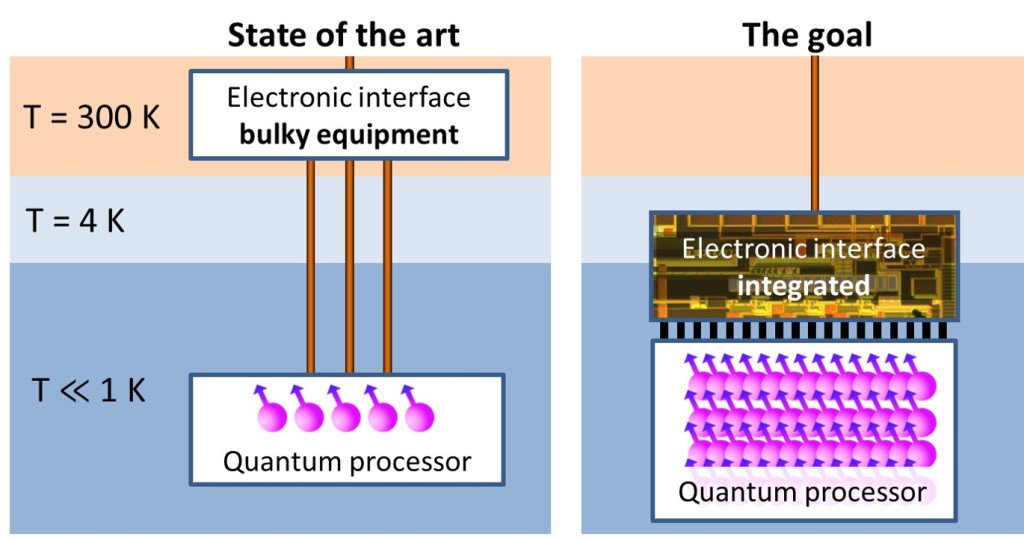

Six speakers from top-notch groups around the world will discuss the challenges and the research opportunities to be addressed on the path to build a quanutm computer with enough computing power to solve relevant problems, such as simulating a quantum systems like complex molecules and materials. The talks will span the whole stack of discipline required to build such a complex machine, ranging from quantum physics, thorugh electrical engineering and circuit design and up to computer architectures and quanutm compilers.

Join the session if you are in Sapporo!

A list of the papers below:

- Semiconductor spin qubits – a scalable platform for quantum computing? L. Schreiber, H. Bluhm, RWTH Aachen University, Germany

- Benefits and Challenges of Designing Cryogenic CMOS RF Circuits for Quantum Computer, M.Babaie1, M. Mehrpoo1, B. Patra1, J. Gong1, J.P.G. van Dijk1, P.A. ‘t Hart1, G. Kiene1, A. Vladimirescu1,2,3, F. Sebastiano1, E. Charbon1,4,5, 1Delft University of Technology, The Netherlands2University of California at Berkeley, U.S.,3Institut Supérieur d’Electronique de Paris, France 4EPFL, Switzerland5Intel, U.S.

- Systems Engineering of Cryogenic CMOS Electronics for Scalable Quantum Computers, C. Degenhardt1, A. Artanov1, V. Christ1, L. Geck1, C. Grewing1, A. Kruth1, D. Liebau1, P. Muralidharan1, D. Nielinger1, P. Schubert1, P. Vliex1, A. Zambanini1, and S. van Waasen1,2 1Forschungszentrum Jülich GmbH, Jülich, Germany2University of Duisburg-Essen, Germany

- Cryogenic support circuits and systems for silicon quantum computers, Torsten Lehmann, UNSW, Australia

- Quantum Accelerated Computer Architectures, L. Riesebos, X. Fu, A. A. Moueddenne, L. Lao, S. Varsamopoulos, I. Ashraf, J. van Someren, N. Khammassi, C. G. Almudever, K. Bertels, Delft University of Technology, The Netherlands

- Reducing the Overhead of Mapping Quantum Circuits to IBM Q Systems, Atsushi Matshuo, Wakaki Hattori and Shigeru Yamashita, Ritsumeikan University, Japan

The papers are already available on IEEExplore.